Protocol decoder:sae_j1850_vpw

Jump to navigation

Jump to search

| |

| Name | SAE J1850 VPW |

|---|---|

| Description | SAE J1850 Variable Pulse Width 1x and 4x. |

| Status | supported |

| License | GPLv2+ |

| Source code | decoders/sae_j1850_vpw |

| Input | logic |

| Output | — |

| Probes | data |

SAE J1850 VPW is one of several signal protocols mandated by OBD2/EOBD legislation, which requires automotive vehicle manufacturers from 1996 (USA) or 2001 (Europe) to provide access to the vehicles data bus via a standard 16 pin SAE J1962 connector. The purpose originally being to allow testing and diagnostics from the "on-board diagnostic" capabilities (which were also required by the legislation), of the control module responsible for the vehicles emission control system (typically the PCM, Powertrain Control Module). However the VPW databus also serves many other purposes.

SAE J1850 came in 2 varieties:

- PWM (Pulse Width Modulation), 41.6 kb/s, typically used by Ford.

- VPW (Variable Pulse Width), 10.4 kb/s, typically used by General Motors.

The way the bits are represented on the bus and voltage level is different between them. This decoder is for the VPW variety.

Example use

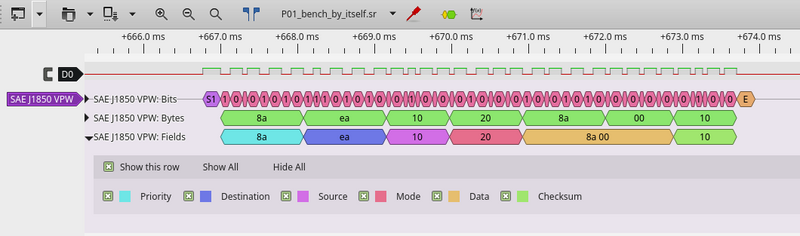

$ sigrok-cli -i P01_bench_by_itself.sr -P sae_j1850_vpw:data=D0 -A sae_j1850_vpw=fields --protocol-decoder-ann-class ... sae_j1850_vpw-1: prio: 88 sae_j1850_vpw-1: dest: 15 sae_j1850_vpw-1: src: 10 sae_j1850_vpw-1: mode: 01 sae_j1850_vpw-1: csum: c8 sae_j1850_vpw-1: prio: 88 sae_j1850_vpw-1: dest: 1b sae_j1850_vpw-1: src: 10 sae_j1850_vpw-1: mode: 10 sae_j1850_vpw-1: data: 00 00 sae_j1850_vpw-1: csum: 46 sae_j1850_vpw-1: prio: 8a sae_j1850_vpw-1: dest: ea sae_j1850_vpw-1: src: 10 sae_j1850_vpw-1: mode: 20 sae_j1850_vpw-1: data: 8a 00 sae_j1850_vpw-1: csum: 10 ...

Resources

- PCM hacking forum thread

- Antus' partial migration, pman92's repo (see the decoders/vpw/ directory)

- pman92's example captures (see the vpw/ directory)

- https://www.irjet.net/archives/V4/i7/IRJET-V4I791.pdf

- http://www.fastfieros.com/tech/vpw_communication_protocol.htm